# **CML Semiconductor Products**

**PRODUCT INFORMATION**

**FX365C** Low-Voltage CTCSS Encoder/ Decoder

Publication D/365C/3 October 1995

#### **Features**

- Low-Voltage (3-Volt) Supply

- 39 Programmable Sub-Audio Tones + NOTONE

- Meets MPT1306 and EIA 220 B

- High Voiceband/CTCSS Isolation

- Separate Sub-Audio and Rx/Tx Audio Paths and Filtering

#### **Applications**

- Mobile Radio Systems

- Community Base Stations

- "Sports Radio" (Japan)

- Sub-Audio Signalling and Selective Calling

- Status and Alarm Systems

- Amateur Radio

FX365C

### **Brief Description**

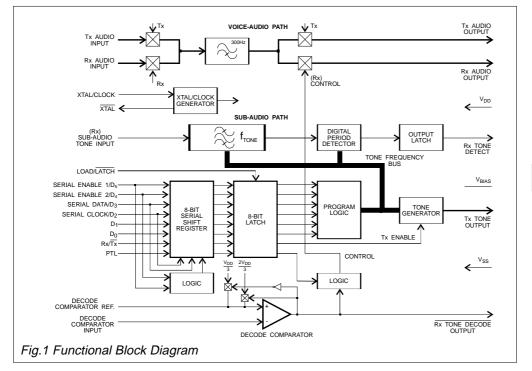

The FX365C is a 3-volt, half-duplex predictive Continuous Tone Controlled Squelch System (CTCSS) encoder/decoder microcircuit. The FX365C has integral voice-band filtering for prefiltering of Tx audio and the rejection of the CTCSS tone in receive.

Under µProcessor control, the FX365C will encode and decode any one of 39 sub-audio frequencies (+NOTONE) in the range 67.0Hz to 250.3Hz. Tone frequencies and all functional commands can be loaded to the device in either pin-selectable 8-bit parallel or serial format.

A separate, Rx/Tx voice-audio path is available with a highpass (sub-audio reject) filter automatically placed in the relevant Rx or Tx voice line. The Rx sub-audio (CTCSS) path contains a (selected tone frequency) bandpass filter and period detector providing a logic level output (Rx Tone Detect) to indicate a successful decode operation.

Rx "Press to Listen" (PTL) and Tx "Squelch-Tail Elimination" functions are available in both command loading modes. The squelch-tail elimination function will provide (Tx tone) phase-reversal to minimise the annoying audio outputs that occur at the receiver on completion of a transmission.

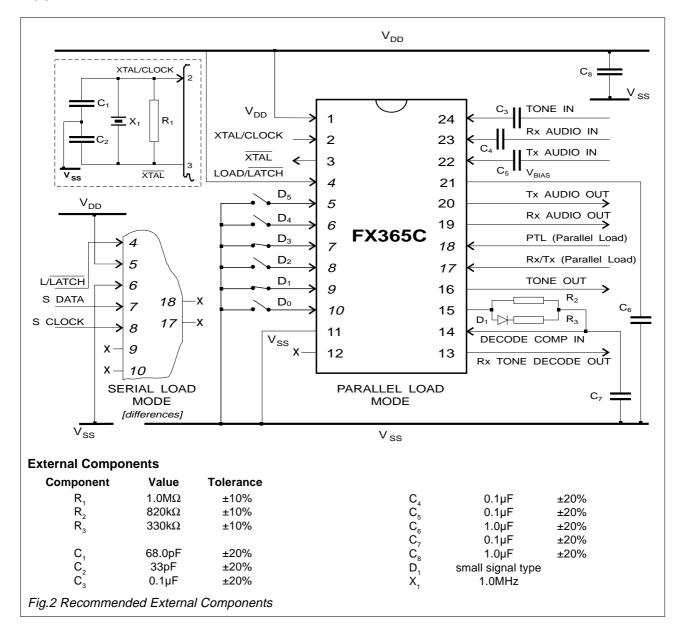

Tone frequencies and filter accuracies are maintained by an on-chip 1.0MHz clock oscillator employing an external crystal or clock pulse input.

The FX365C, which exhibits high audio and subaudio performance with low falsing, is available in 24pin DIL and small outline SMD packages.

### **Pin Number**

Function

| DW, J, LG and LS package styles                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{pp}$ : Positive supply rail. A single stable supply is required; levels and voltages within the FX365C are dependent upon this supply.<br>This pin should be decoupled to $V_{ss}$ by a capacitor located close to the pin.                                                                                                                                                                                                                                                                         |

| Xtal/Clock: Input to the on-chip inverter; used with a 1.0MHz Xtal or external clock source.                                                                                                                                                                                                                                                                                                                                                                                                            |

| <b>Xtal:</b> Output of the on-chip clock oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                           |

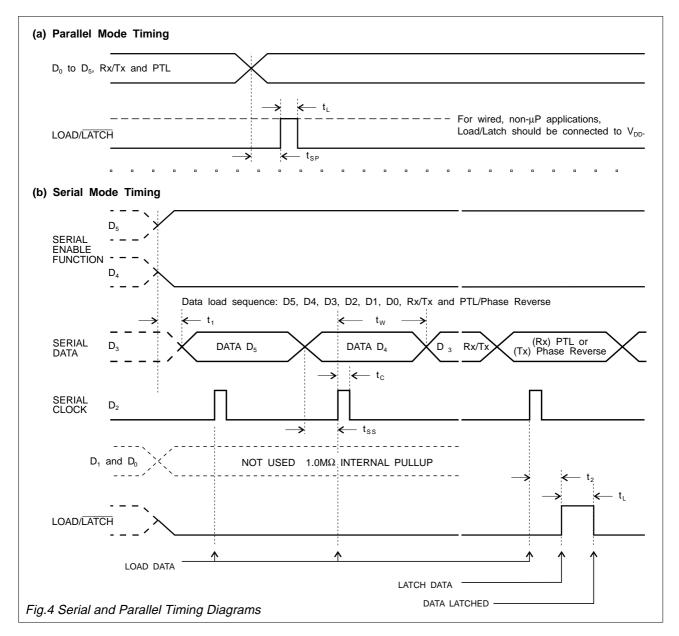

| <b>Load/Latch:</b> Controls 8 on-chip latches and is used to latch $Rx/Tx$ , $PTL$ , $D_0 - D_5$ . This pin is internally pulled to $V_{DD}$ . A logic '1' applied to this input places the 8 latches into a 'transparent' mode. A logic '0' applied to this input places the 8 latched' mode. In parallel mode data is loaded and latched by a logic '1' to '0' transition (see Figure 4a). In serial mode data is loaded and latched by a '0' to '1' to '0' strobe pulse on this pin (see Figure 4b). |

| <b>D</b> <sub>2</sub> / <b>Serial Enable 1:</b> Data input D <sub>5</sub> (Parallel Mode); Serial Enable 1 (Serial Mode).<br>A logic 'l' applied to this input, together with a logic '0' applied to D <sub>4</sub> /Serial Enable 2, will put the device into 'Serial Mode' (see Figure 4b). This pin is internally pulled to $V_{DD}$ .                                                                                                                                                               |

| <b>D</b> <sub>4</sub> /Serial Enable 2: Data input D <sub>4</sub> (Parallel Mode); Serial Enable 2 (Serial Mode).<br>A logic '0' applied to this input, together with a logic '1' applied to D <sub>5</sub> /Serial Enable 1, will place the device into 'Serial Mode' (see Figure 4b). This pin internally pulled to $V_{DD}$ .                                                                                                                                                                        |

| <b>D</b> <sub>3</sub> /Serial Data: Data input D <sub>3</sub> (Parallel Mode); Serial Data Input (Serial Mode).<br>In Serial Mode this pin becomes the serial data input for D <sub>5</sub> - D <sub>0</sub> , Rx/Tx, PTL (see Figure 4b). D <sub>5</sub> is clocked-in first and PTL last. This pin internally pulled to $V_{DD}$ .                                                                                                                                                                    |

| <b>D</b> <sub>2</sub> /Serial Clock: Data input D <sub>2</sub> (Parallel Mode); Serial Clock Input (Serial Mode).<br>In Serial Mode this pin becomes the Serial Clock input. Data is clocked on the positive-going edge (see Figure 4b). This pin is internally pulled to $V_{DD}$ .                                                                                                                                                                                                                    |

| <b>D</b> <sub>1</sub> : Data input D <sub>1</sub> (Parallel Mode); Not Used (Serial Mode). This pin is internally pulled to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                  |

| <b>D</b> <sub>0</sub> : Data input D <sub>0</sub> (Parallel Mode); Not Used (Serial Mode). This pin is internally pulled to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                  |

| V <sub>ss</sub> : Negative supply (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <b>Decode Comparator Ref.</b> (I/P): Internally biased to $V_{DD}/3$ or $2V_{DD}/3$ via 1.0M $\Omega$ resistors depending<br>on the logical state of the Tone Decode Output pin, this input provides the decode comparator<br>reference voltage; switching of bias voltages provides hysteresis to reduce 'chatter' under marginal<br>conditions. Tone Decode Output = logic '1' will place this input to $2V_{DD}/3$ bias, a logic '0' will bias this<br>input to $V_{DD}/3$ .                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Pin Number **Function** FX365C DW and J package styles. **Rx Tone Decoder** (O/P): The gated output of the on-chip Decode Comparator. 13 This output is used to gate the Rx Audio path. A logic '0' output on this pin indicates a successful decode and indicates that the 'Decode Comparator Input' pin is more positive than the 'Decode Comparator Ref' input (see Table 1). Decode Comparator Input: The inverting input of the Decode Comparator. This pin is to be 14 connected to the Rx Tone Detect pin via external integrating components as shown in Figure 2. Rx Tone Detect (O/P): In the Rx mode this output will go to a logic '1' during a successful decode 15 (Table 1). This pin is to be connected to the Decode Comparator Input via the external integrating circuitry as shown in Figure 2. Tx Tone Output: A low-impedance emitter-follower source, under the control of the Rx/Tx pin, of the 16 CTCSS sinewave. This output, when not transmitting a sub-audio tone, may be set to a V<sub>pr</sub>/(2-0.7)V bias or open-circuit as described in Table 1. **Rx/Tx:** This input (Parallel Mode) selects Rx or Tx modes (see Figure 2). Logic '1' = Rx; 17 logic '0' = Tx. In Serial Mode this (Rx or Tx) function is serially loaded via pin 7 (Serial Data) and this pin not used. This pin is internally pulled to $V_{_{DD}}$ via a 1M $\Omega$ resistor (Rx operaion). PTL: A dual-function input. In the parallel load mode, Rx operation: A logic '1' provides a "Press To 18 Listen" function by overriding the tone-squelch and enabling the audio path. In the parallel load mode, Tx operation: A logic '1' provides a "Squelch Tail Elimination" function by reversing the phase of the transmitting sub-audio tone; the phase reversal function should be applied by a suitable timing circuit. In the serial load mode (Rx and Tx) these functions are loaded via the serial data word at pin 7. Rx Audio Output: The high-pass filtered 'Received Audio' output. This pin outputs audio when Rx 19 Tone Decode = '0', or PTL = '1' or 'Notone' is programmed (Table 2). In Tx Mode this pin is biased to V<sub>DD</sub>/2. Tx Audio Output: The high-pass filtered 'Transmit Audio' output. In Tx mode this pin outputs audio 20 present at the Tx Audio Input by opening the Tx audio path. In Rx mode this pin is biased to V<sub>DD</sub>/2. $V_{\text{BIAS}}$ : The output of the on-chip analogue bias circuitry. Held internally at $V_{\text{DD}}/2$ , this pin should be 21 externally decoupled to $V_{ss}$ . Tx Audio Input: The Tx Audio Input pin. Tx voice-band audio may be prefiitered, using the Voice 22 Audio Path, thus helping to avoid talk-off due to the intermodulation of speech frequencies with the transmitted CTCSS tone. The Tx Audio Path may also be used to pre-filter speech when employing 'scramblers' which could introduce noise into the low frequency band. This pin is internally biased to V<sub>DD</sub>/2. Rx Audio Input: The input to the Voice Audio high-pass filter in the Rx Mode. 23 This pin is internally biased to $V_{DD}/2$ . **Tone Input:** The input to the CTCSS tone detector and is internally biased to $V_{pp}/2$ . 24

### **Application Information**

| Input Pin Condition Output Pin |       |     |                          | in Condition Result and/or Function |                   |                       |                              |                             |                            |                             |            |

|--------------------------------|-------|-----|--------------------------|-------------------------------------|-------------------|-----------------------|------------------------------|-----------------------------|----------------------------|-----------------------------|------------|

| D₀ to D₅                       | Rx/Tx | PTL | Decode<br>Comp.<br>Input | Rx Tone<br>Detect                   | Rx Tone<br>Decode | Tone<br>Tx<br>Enabled | Tx Tone<br>Phase<br>Reversed | Tx Audio<br>Path<br>Enabled | Tone<br>Decoder<br>Enabled | Rx Audio<br>Path<br>Enabled |            |

| TONE                           | 0     | 0   | х                        | 0                                   | 1                 | Yes                   | No                           | Yes                         | No                         | No (bias)                   | <b>1</b> A |

| TONE                           | 0     | 1   | х                        | 0                                   | 1                 | Yes                   | Yes                          | Yes                         | No                         | No (BIAS)                   | 1в         |

| NOTONE                         | 0     | х   | х                        | 0                                   | 1                 | No (BIAS)             | х                            | Yes                         | No                         | No (BIAS)                   | 2          |

| TONE                           | 1     | 0   | 0                        | 0                                   | 1                 | No(o/c)               | х                            | No                          | Yes                        | YES                         | 3a         |

| TONE                           | 1     | 1   | 0                        | 0                                   | 1                 | No (o/c)              | х                            | No                          | Yes                        | Yes                         | 3в         |

| TONE                           | 1     | х   | 1                        | 1                                   | 0                 | No (o/c)              | х                            | No                          | Yes                        | Yes                         | 4          |

| NOTONE                         | 1     | х   | х                        | x                                   | 0                 | No (o/c)              | х                            | No                          | Yes                        | Yes                         | 5          |

NOTES

1A Normal tone transmit condition.

1B Tone Tx with phase reversed.

2 NOTONE programmed in Tx mode; tone transmit output set to  $V_{DD}/2$  -(0.7v). Tx audio path enabled.

3A Normal decode standby.

3B Normal decode standby with PTL used to enable audio.

4 Normal 'decode of correct CTCSS tone' condition; PTL has no effect.

5 NOTONE programmed in Rx mode; tone transmit output (o/c). Rx audio path enabled.

Table 1 Combinations of Input/Output Conditions

x = don't care

## Application Information .....

| Nominal<br>Freq (Hz) | FX365C<br>Freq. (Hz) | Δfo %          | D      | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | $D_4$  | D5 |

|----------------------|----------------------|----------------|--------|----------------|----------------|----------------|--------|----|

| 67.0                 | 67.05                | +0.7           | 1      | 1              | 1              | 1              | 1      | 1  |

| 69.3                 | 69.32                | +0.03          | 1      | 0              | 0              | 1              | 1      | 1  |

| 71.9                 | 71.90                | 0.0            | 1      | 1              | 1              | 1              | 1      | 0  |

| 74.4                 | 74.35                | -0.07          | 0      | 1              | 1              | 1              | 1      | 1  |

| 77.0                 | 76.96                | -0.05          | 1      | 1              | 1              | 1              | 0      | 0  |

| 79.7                 | 79.77                | +0.09          | 1      | 0              | 1              | 1              | 1      | 1  |

| 82.5                 | 82.59                | +0.10          | 0      | 1              | 1              | 1              | 1      | 0  |

| 85.4                 | 85.38                | -0.02          | 0      | 0              | 1              | 1              | 1      | 1  |

| 88.5                 | 88.61                | +0.13          | 0<br>0 | 1              | 1              | 1              | 0      | 0  |

| 91.5                 | 91.58                | +0.09          | 1      | 1              | Ö              | 1              | 1      | 1  |

| 94.8                 | 94.76                | -0.04          | 1      | 0              | 1              | 1              | 1      | 0  |

| 97.4                 | 97.29                | -0.11          | 0      | 1              | 0              | 1              | 1      | 1  |

| 100.0                | 99.96                | -0.04          | 1      | 0              | 1              | 1              | 0      | 0  |

| 103.5                | 103.43               | -0.07          | 0      | 0              | 1              | 1              | 1      | 0  |

| 103.3                | 107.15               | -0.05          | 0      | 0              | 1              | 1              | 0      | 0  |

| 1107.2               | 1107.15              | -0.12          | 1      | 1              | 0              | 1              | 1      | 0  |

| 114.8                | 114.64               | -0.12          | 1      | 1              | 0              | 1              | 0      | 0  |

| 114.8                | 118.80               | -0.14          | 0      | 1              | 0              | 1              | 1      | 0  |

|                      |                      |                |        | -              |                | 1              |        |    |

| 123.0<br>127.3       | 122.80               | -0.17<br>-0.17 | 0<br>1 | 1              | 0              | 1              | 0<br>1 | 0  |

| -                    | 127.08               | -              | •      | 0              | 0              | -              | -      | 0  |

| 131.8                | 131.67               | -0.10          | 1      | 0              | 0              | 1              | 0      | 0  |

| 136.5                | 136.61               | +0.08          | 0      | 0              | 0              | 1              | 1      | 0  |

| 141.3                | 141.32               | +0.02          | 0      | 0              | 0              | 1              | 0      | 0  |

| 146.2                | 146.37               | +0.12          | 1      | 1              | 1              | 0              | 1      | 0  |

| 151.4                | 151.09               | -0.20          | 1      | 1              | 1              | 0              | 0      | 0  |

| 156.7                | 156.88               | +0.11          | 0      | 1              | 1              | 0              | 1      | 0  |

| 162.2                | 162.31               | +0.07          | 0      | 1              | 1              | 0              | 0      | 0  |

| 167.9                | 168.14               | +0.14          | 1      | 0              | 1              | 0              | 1      | 0  |

| 173.8                | 173.48               | -0.19          | 1      | 0              | 1              | 0              | 0      | 0  |

| 179.9                | 180.15               | +0.14          | 0      | 0              | 1              | 0              | 1      | 0  |

| 186.2                | 186.29               | +0.05          | 0      | 0              | 1              | 0              | 0      | 0  |

| 192.8                | 192.86               | +0.03          | 1      | 1              | 0              | 0              | 1      | 0  |

| 203.5                | 203.65               | +0.07          | 1      | 1              | 0              | 0              | 0      | 0  |

| 210.7                | 210.17               | -0.25          | 0      | 1              | 0              | 0              | 1      | 0  |

| 218.1                | 218.58               | +0.22          | 0      | 1              | 0              | 0              | 0      | 0  |

| 225.7                | 226.12               | +0.18          | 1      | 0              | 0              | 0              | 1      | 0  |

| 233.6                | 234.19               | +0.25          | 1      | 0              | 0              | 0              | 0      | 0  |

| 241.8                | 241.08               | -0.30          | 0      | 0              | 0              | 0              | 1      | 0  |

| 250.3                | 250.28               | -0.01          | 0      | 0              | 0              | 0              | 0      | 0  |

| NOTONE               | NOTONE               |                | 0      | 0              | 0              | 0              | 1      | 1  |

| Serial Input I       | Mode                 |                | х      | х              | Clock          | Data           | 0      | 1  |

|                      | ne Programm          | ing Informatio | on     |                |                |                |        |    |

### **Specification**

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

| Supply voltage                  |                    | -0.3 to 7.0V                     |

|---------------------------------|--------------------|----------------------------------|

| Input voltage at any pin (ref V | <sub>s</sub> = 0V) | -0.3 to (V <sub>DD</sub> + 0.3V) |

| Sink/source current (supply pil |                    | +/- 30mA                         |

| (other pins                     | 6)                 | +/- 20mA                         |

| Total device dissipation @ T    | ₽ 25°C             | 800mW Max.                       |

| Derating                        |                    | 10mW/°C                          |

| Operating temperature range:    | FX365C J           | -40°C to +85°C (cerdip)          |

|                                 | FX365C DW          | -40°C to +85°C (plastic)         |

| Storage temperature range:      | FX365C J           | -55°C to +125°C (cerdip)         |

|                                 | FX365C DW          | -40°C to +85°C (plastic)         |

#### **Operating Limits**

All device characteristics are measured under the following conditions unless otherwise specified:  $V_{DD} = 3.3V$ .  $T_{AMB} = 25^{\circ}$ C. Xtal/Clock  $f_0 = 1.0$ MHz. Signal 0dB ref: = 180mVrms. Composite Signal = 1.0kHz Audio Tone at 0dB, Noise at -12.0dB (gaussian white noise, band-limited to 6.0kHz), Programmed CTCSS Tone at -20dB.

| Characteristics                                   | See Note | Min.  | Тур.  | Max.  | Unit            |

|---------------------------------------------------|----------|-------|-------|-------|-----------------|

| Static Characteristics                            |          |       |       |       |                 |

| Supply Voltage (V <sub>pp</sub> )                 |          | 3.0   | 3.3   | 5.5   | V               |

| Supply Current                                    |          |       |       |       |                 |

| (Tx)                                              |          | -     | 1.5   | -     | mA              |

| (Rx)                                              |          | -     | 1.5   | -     | mA              |

| Sub-Audio Tone Input Impedance                    |          | -     | 1.0   | -     | MΩ              |

| Tx Tone Output Impedance                          |          | -     | 4.0   | -     | kΩ              |

| Voice-Audio Input Impedance                       |          | -     | 1.0   | -     | MΩ              |

| Voice-Audio Output Impedance                      |          | -     | 1.0   | -     | kΩ              |

| Digital Input Impedance                           | 1        | -     | 1.0   | -     | MΩ              |

| Input Logic '1'                                   | 1        | 70.0  | -     | -     | $%V_{DD}$       |

| Input Logic '0'                                   | 1        | -     | -     | 30.0  | $%V_{DD}^{DD}$  |

| Output Logic '1', source = 0.1mA                  | 2        | 80.0  | -     | -     | $%V_{DD}^{DD}$  |

| Output Logic '0', sink = 0.1 mA                   | 2        | -     | -     | 20.0  | $%V_{DD}^{DD}$  |

| Dynamic Characteristics                           |          |       |       |       | 00              |

| Tone Decoder                                      |          |       |       |       |                 |

| Decode Input Signal Level                         | 3        | -20.0 | -     | -     | dB              |

| Decode Response Time                              | 3, 6     | -     | -     | 250   | ms              |

| De-Response Time                                  | 3, 6     | -     | -     | 250   | ms              |

| Decode Selectivity                                | 3        | ±0.5  | -     | ±3.0  | %f <sub>o</sub> |

| Tone Encoder                                      |          |       |       |       | 0               |

| Tx Tone Output Level                              |          | -     | 627   | -     | mVrms           |

| Tx Tone Frequency Accuracy (f <sub>o</sub> error) |          | -0.3  | -     | +0.3  | %f <sub>o</sub> |

| Risetime to 90% (nominal output)                  |          |       |       |       | 0               |

| f <sub>o</sub> > 100Hz                            | 4        | -     | 55.0  | -     | ms              |

| f <sub>o</sub> < 100Hz                            | 4        | -     | 70.0  | -     | ms              |

| Tone Output Load Current                          |          | -     | -     | 5.0   | mA              |

| Total Harmonic Distortion                         |          | -     | 2.0   | 5.0   | %               |

| Output Level Variation Between Tones              |          | -     | 0.1   | -     | dB              |

| Spurious Emissions                                |          | -     | -     | -48.0 | dB              |

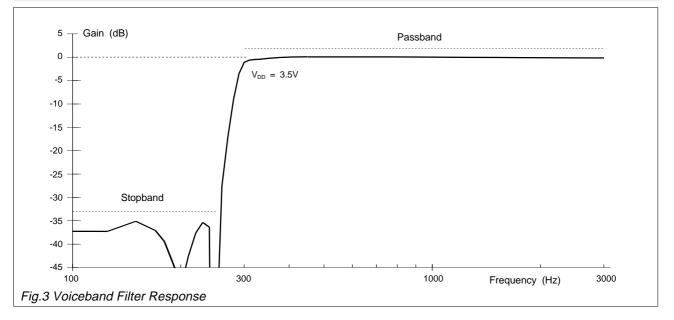

| Voice-Audio Filter and Path                       |          |       |       |       |                 |

| Passband Frequencies                              |          | 300   |       | 3000  | Hz              |

| Passband Gain                                     |          |       |       |       |                 |

| at 1.0kHz                                         |          | -     | 0     | -     | dB              |

| w.r.t. 1.0kHz                                     |          | -2.0  | -     | 0.5   | dB              |

| Total Harmonic Distortion                         | 5        | -     | 2.0   | 5.0   | %               |

| Stopband Frequencies                              | -        | -     | -     | 250   | Hz              |

| Stopband Attenuation                              |          | 33.0  | 36.0  |       | dB              |

| Output Noise Level (Input a.c. Short Cct)         | 7        | -     | -54.0 | -48.0 | dB              |

| SINAD                                             | 8        | 36.0  | 40.0  | -     | dB              |

|                                                   |          |       |       |       |                 |

### Specification .....

| Characteristics                                 | See Note | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|----------|------|------|------|------|

| Serial/Parallel Inputs                          |          |      |      |      |      |

| Parallel Set-Up Time (t <sub>sp</sub> )         |          | 400  | -    | -    | ns   |

| Load/Latch Pulse Width (t,)                     |          | 400  | -    | -    | ns   |

| Serial Clock Pulse Width (t <sub>c</sub> )      |          | 400  | -    | -    | ns   |

| Serial Set-Up Time (t <sub>ss</sub> )           |          | 400  | -    | -    | ns   |

| Serial Enable Time (t,)                         |          | 400  | -    | -    | ns   |

| Serial Load/Latch Set-Up Time (t <sub>2</sub> ) |          | 400  | -    | -    | ns   |

| Serial Clock Frequency                          |          | -    | 1.0  | -    | MHz  |

#### Notes

- 1. Refers to Rx/Tx, PTL, Decode Comparator Input, D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>, D<sub>4</sub>, D<sub>5</sub> inputs.

- 2. All logic outputs.

- 3. Composite Signal test condition.

- Any programme tone and RL =  $600\Omega$ . CL = 15pF. Includes response to a phase-reversal instruction. 4.

- 5. 1 kHz reference = 0 dB.

- $\rm f_{\rm o}$  > 100Hz, (for 100Hz >f\_{\rm o}>67Hz: t = (100/f\_{\rm o} Hz) x 250ms). Measured in a 30kHz bandwidth. 6.

- 7.

- For an input level of 180mVrms at 1.0kHz, in a 30kHz measurement bandwidth. 8.

### **Package Outlines**

The FX365C is available in the package styles outlined below. Mechanical package diagrams and specifications are detailed in Section 10 of this document.

Pin 1 identification marking is shown on the relevant diagram and pins on all package styles number anti-clockwise when viewed from the top.

#### **Handling Precautions**

The FX365C is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

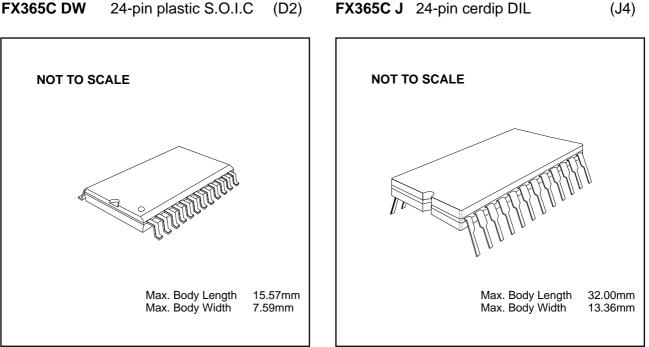

#### **FX365C DW** 24-pin plastic S.O.I.C (D2)

### **Ordering Information**

| FX365C DW 24-pin plastic S.O.I.C. | (D2) |

|-----------------------------------|------|

|                                   |      |

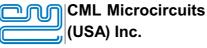

| <b>FX365C J</b> 24 | l-pin cerdip DIL | (J4) |

|--------------------|------------------|------|

|--------------------|------------------|------|

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.

### **CML Product Data**

In the process of creating a more global image, the three standard product semiconductor companies of CML Microsystems Plc (*Consumer Microcircuits Limited (UK), MX-COM, Inc (USA) and CML Microcircuits (Singapore) Pte Ltd)* have undergone name changes and, whilst maintaining their separate new names (*CML Microcircuits (UK) Ltd, CML Microcircuits (USA) Inc and CML Microcircuits (Singapore) Pte Ltd*), now operate under the single title CML Microcircuits.

These companies are all 100% owned operating companies of the CML Microsystems Plc Group and these changes are purely changes of name and do not change any underlying legal entities and hence will have no effect on any agreements or contacts currently in force.

#### **CML Microcircuits Product Prefix Codes**

Until the latter part of 1996, the differentiator between products manufactured and sold from MXCOM, Inc. and Consumer Microcircuits Limited were denoted by the prefixes MX and FX respectively. These products use the same silicon etc. and today still carry the same prefixes. In the latter part of 1996, both companies adopted the common prefix: CMX.

This notification is relevant product information to which it is attached.

Company contact information is as below:

Oval Park, Langford, Maldon, Essex, CM9 6WG, England Tel: +44 (0)1621 875500 Fax: +44 (0)1621 875600 uk.sales@cmlmicro.com www.cmlmicro.com

COMMUNICATION SEMICONDUCTORS

4800 Bethania Station Road, Winston-Salem, NC 27105, USA Tel: +1 336 744 5050, 0800 638 5577 Fax: +1 336 744 5054 us.sales@cmlmicro.com www.cmlmicro.com

No 2 Kallang Pudding Road, 09-05/ 06 Mactech Industrial Building, Singapore 349307 Tel: +65 7450426 Fax: +65 7452917 sg.sales@cmlmicro.com www.cmlmicro.com